Portál AbcLinuxu, 7. května 2024 16:43

Minule jsme si ukázali, co je to proces. Dnešní článek bude o registrech - co to je, jak je popsat ve VHDL a proč jsou tak důležité.

Všechny naše dosavadní obvody měly jeden společný rys. Neobsahovaly žádný paměťový prvek, takže hodnoty na výstupu byly závislé pouze na vstupních signálech. Takovéto obvody nazýváme kombinační. Skládají se pouze z logických členů (AND, OR, NOT, ...) a neobsahují zpětné vazby. Naproti tomu obvody, které obsahují paměťové prvky, se nazývají sekvenční. Jejich výstup není určen pouze vstupními signály, ale i vnitřním stavem obvodu (stavem jednotlivých paměťových prvků).

Jak jsme již naznačili minule (Jak se píše procesor - 3 (Procesy)),

jako paměťový prvek budeme využívat pouze registr (tzn. nebudeme tvořit

zpětné vazby v logice). Podívejme se, jak můžeme registr vytvořit pomocí

VHDL. Využijeme k tomu entitu example_2 podobnou entitě z

minulého dílu s tím rozdílem, že obsahuje navíc dva vstupní signály -

RESET a CLK.

ENTITY example_2 IS

PORT (

CLK, RESET: in std_logic;

I1, I2: in std_logic;

O: out std_logic

);

END example_2;

ARCHITECTURE arch_3 OF example_2 IS

BEGIN

p_1: process (RESET, CLK)

begin

if (RESET = '1') then -- asynchronni reset

O <= '0';

elsif (CLK'event and CLK = '1') then -- reakce na vz. hranu

O <= I1 and I2;

end if;

end process;

END arch_3;

Do procesu jsme vložili dvě sekce. Jednu reagující na reset a jednu na vzestupnou hranu hodin. VHDL zápis konkrétně znamená:

RESET '1', spusť první sekci

příkazů (to odpovídá činnosti asynchronního resetu v registru - nastavení

implicitních hodnot po startu systému).elsif) spusť druhou sekci příkazů, ale

pouze v případě, že došlo ke změně signálu CLK a tento signál

má hodnotu '1' (odpovídá náběžné hraně). Jinak řečeno, přiřaď

do výstupního signálu určenou logickou funkci, ale pouze v okamžiku

náběžné hrany hodin. Proto tento zápis vloží na konec cesty každého

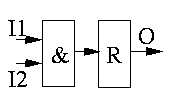

výstupního signálu registr.Náš příklad bude tedy vypadat takto:

Podmíněný příkaz tvořící registr (if RESET... elsif

CLK...) je dobré brát pokud možno dogmaticky. Dnešní

programovatelné obvody důrazně dělí obvod na logiku a registry a každý

zásah do této části VHDL kódu může tuto strukturu narušit. Programovatelné

obvody také mají dedikované hodinové rozvody, proto, pokud si nejsme

jisti, je dobré používat v celém obvodu pouze jeden signál

CLK.

Nyní známe takřka všechno, co je třeba k napsání procesoru ve VHDL. Navrhněme proto další entitu - sadu registrů. Zvolme jednoduchou variantu sady čtyř osmibitových registrů, kde jedinou funkcí bude zápis do registrů a čtení z nich.

ENTITY register_set IS

PORT (

CLK, RESET: in std_logic;

I: in std_logic_vector(7 downto 0);

O: out std_logic_vector(7 downto 0);

ADDR: in std_logic_vector(1 downto 0);

WR: in std_logic

);

END register_set;

ARCHITECTURE behavioral OF register_set IS

signal R1, R2, R3, R4: std_logic_vector(7 downto 0);

BEGIN

p_1: process (RESET, CLK)

begin

if (RESET = '1') then -- asynchronni reset

R1 <= (others => '0');

R2 <= (others => '0');

R3 <= (others => '0');

R4 <= (others => '0');

elsif (CLK'event and CLK = '1') then -- reakce na vz. hranu

if WR = '1' then

if A = "00" then

R1 <= I;

elsif A = "01" then

R2 <= I;

elsif A = "10" then

R3 <= I;

else

R4 <= I;

end if;

end if;

end if;

end process;

O <= R1 when A = "00" else

R2 when A = "01" else

R3 when A = "10" else

R4;

END behavioral;

V entitě definujeme vstupní a výstupní signály. CLK a

RESET jsou důležité pro synchronizaci registrů.

I a O jsou vstupní a výstupní datové sběrnice,

A vybírá jeden ze čtyř registrů. Pomocí signálu

WR zapisujeme do jednotlivých registrů. Signál pro čtení

není třeba, na výstupní sběrnici je vždy hodnota aktivního registru.

V deklarační části architektury si definujeme čtyři pomocné osmibitové

signály, pomocí kterých vytvoříme vlastní registry. Hlavní část těla

architektury tvoří proces, který implikuje vytvoření registrů a realizuje

zápis. Kód nám říká, že v případě aktivního signálu WR má být

přiřazena hodnota sběrnice I do jednoho ze signálů

R1 - R4. Toto přiřazení se má provést pouze v

okamžiku náběžné hrany signálu CLK. Pro syntezátor to tedy

znamená vytvoření čtyř osmibitových registrů se vstupem I,

výstupem R1 - R4 a povolovacím signálem (chip

enable, CEx) tvořeným ze signálů WR a

A.

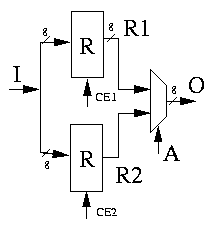

Výstup O je tvořen pomocí signálu WHEN. V

tomto případě to bude multiplexor, který vybírá výstup jednoho z registrů

v závislosti na adrese A.

Na obrázku je znázorněno zjednodušené schéma pro 2 registry:

ISSN 1214-1267, (c) 1999-2007 Stickfish s.r.o.