Portál AbcLinuxu, 30. dubna 2026 19:29

Velkým překvapením je nejnovější tvrzení Toshiby, že QLC NAND flash čipy mohou dosahovat stejné životnosti, tedy počtu Program/Erase cyklů, jako TLC NAND flash. Uvidíme, jakou se ukáže realita let nadcházejících, nicméně toto otevírá dveře k příchodu levných QLC SSD pro běžné spotřebitele. Dále se podíváme na vícečipová řešení, která vyvíjí Nvidia, či situaci s budoucí architekturou CPU Intel.

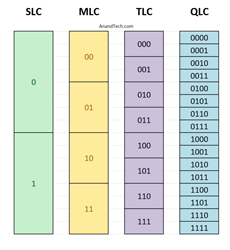

Nejprve je nutné si opět připomenout, jak se to s SLC - MLC - TLC - QLC čipy má. To, že paměťová buňka v případě SLC uchovává buď logickou 1, nebo logickou 0, znamená, že musí být u ní zápisem možné definovat dvě konkrétní hodnoty napětí (s určitým ± od optimálního středu hodnoty). To je poměrně snadné. Pro MLC jsou ale v buňce uchovávány už dva bity, tedy ukládají se hodnoty z množiny 00 / 01 / 10 / 11. Je tedy potřeba rozlišovat při zápisu / čtení čtyři hladiny napětí dané paměťové buňky. Pro TLC je těchto hodnot již 8 a pro QLC 16. Proto čím více bitů v buňce, tím menší životnost zápisu daného typu NAND flash čipu, neboť NAND flash čipy postupem doby / používáním degradují a čím více bitů, tím dříve přestane být řadič schopen rozlišovat ony hladiny napětí. Teoreticky je klidně možné, že jednoho dne někdo přijde s 5bitovými, 6bitovými, nebo třeba 20bitovými NAND flash čipy, nicméně o reálnosti a smysluplnosti takového počínání si jistě každý umí udělat představu. Už jen z toho prostého faktu, že když je v buňce potřeba přepsat jediný bit, znamená to u QLC nutnost „přepsat všech 16 hodnot“, neboť se musí do buňky „uložit“ jiná hodnota jejího napětí.

No ale k věci. Toshiba nedávno uvedla nové QLC čipy, dokonce vrstvené. Jejich kapacita je 768 Gbitů, tedy 96 GB / čip. Parádní věc pro paměťové karty a teoreticky i SSD – vždyť do 2,5palcového SATA SSD se dávalo i 8 čipů (u jednoPCB konstrukce). Primárně se využití nových QLC čipů očekává právě v paměťových kartách, tabletech, smartphonech či jiném embedded použití, nicméně mělo by dojít jak na spotřebitelská, tak enterprise (!) SSD.

QLC čipy Toshiby mají dosahovat až 1000 P/E cyklů. To je podstatně více než všeobecně předpokládaných 100 až 150, což by byla hodnota odpovídající tomu, kam se až dosud vyvíjela sekvence SLC → MLC → TLC s přihlédnutím k používání výrobních procesů o stále méně nanometrech. Zatím není jasné, jak toho Toshiba chce dosahovat. Třeba vymysleli nějaký další efektivnější způsob rozkládání zátěže zápisu mezi buňky, třeba vymysleli ještě lepší algoritmy pro detekci a korekci chyb při čtení (aktuálně Toshiba používá vlastní Quadruple Swing-By Codes ECC), nicméně ani tak nelze vysvětlit desetinásobný nárůst. Je možné, že se zde bavíme o přeci jen podstatně konzervativnějšímu výrobnímu procesu ve spojení s vrstvením, nicméně to by zase částečně mazalo ekonomickou výhodnost přechodu na QLC. Nicméně také může jít o skutečnost, že čipy jsou kapacitně výrazně větší než 768 Gbit s tím, že mají vyšší rezervu pro realokaci vadných bloků. Součet všech těchto parametrů může vést k 1000 P/E cyklům.

Toshiba začátkem měsíce zahájila dodávky vzorků QLC čipů partnerům pro další vývoj SSD a jejich řadičů. Mezi velkými zájemci o QLC je mimo jiné Facebook, který by je rád nasadil v rámci svého cold storage (kde mimo jiné aktuálně používá i ztenčené BDXL disky).

Jak naznačují v poslední době zejména procesory od AMD, idea návratu k vícečipovým grafikám bude do budoucna lukrativní. AMD má jako základ architekturu Zen, kde základním procesorem je 8jádrový modul v jednom fyzickém čipu. Od něj se odvíjí varianty vyšší, včetně nedávno představených procesorů Epyc, které nesou tyto moduly čtyři, a tedy nabízí celkem 32 procesorových jader a patřičně navýšené další parametry, ať již jde o 8kanálový paměťový řadič, nebo 128 PCI Express linek přímo v CPU. To vše díky použití čtyř čipů v rámci jednoho velkého procesorového pouzdra osazovaného do obří „patice“.

Ač Nvidia stále dokáže posouvat hranice možného, co do počtu tranzistorů v čipu a zejména co do velikosti (aktuální největší firemní GPU má více než 20 miliard tranzistorů), nejde o cestu optimální pro většinu trhu, pro běžné zákazníky. To dobře naznačuje konkurenční AMD, která raději dříve uvádí nižší typy GPU (např. Radeon RX 480), přičemž velký hi-end následuje až s výrazným zpožděním.

Nvidia se proto ve výzkumu vážně zabývá použitím této „epycové“ techniky. Multi-Chip Module pro GPU (MCM-GPU) není principiálně nic nového, ale pro 4k / 8k / VR éru může být řešením, jak mít na grafické kartě výkon ultra-obřího GPU za použití menších čipů s dobrou výtěžností výroby.

Nový výzkum spolupořádá Nvidia, Arizona State University, University of Texas v Austinu a Barcelona Supercomputing Center. Rozdíl oproti CPU s jednotkami až desítkami CPU jader je v tom, že GPU mají už dnes tisíce malých výpočetních jader, a tak celková komplexnost budoucích vícečipových GPU řešení půjde do desítek tisíc jader, výhledově stovek tisíc jader. Aktuálně simulované řešení u Nvidie je zhruba 4,5× větší než největší GPU Pascal na trhu. Výkonový nárůst oproti (hypotetickému) monolitickému čipu není lineární, přesto se podle všeho vyplatí. Kompletní studie je v případě zájmu k dispozici na webu Nvidie.

Čas od času i Intel sahá po nových neokoukaných tvářích s novými neotřelými nápady. Čas od času si s AMD přetáhnou nějaké ty vývojáře CPU architektur, zkrátka nic zvláštního. Každopádně od dob Intel Core se toho mezi procesorovými architekturami Intelu až tak moc nezměnilo (nové instrukční sady samozřejmě přicházely, ale jádro základních principů fungování Intelích CPU zůstává podobné už řadu let). Ostatně i současné procesory sám Intel prezentuje jako „Core 7. generace“ apod. Je tedy čas na nějakou revoluční změnu.

Pokud pomineme Pentium 4 (což byl opravdu hloupý Barrettův úlet, dlužno dodat, že asi v té době nemohl tušit všechny souvislosti, nemluvě o fenoménu jménem Rambus), tak se Intelu celkem přechody na nové architektury daří. V jejich vývoji se střídají v zásadě dva týmy, jeden americký a druhý izraelský. Intel se nyní připravuje na událost, která nastane až za jednotky let, na uvedení další zbrusu nové a principiálně odlišné architektury CPU. A tak nabírá nové inženýry do týmu v americkém Hillsboro (stát Oregon). Dobré na tom je to, že je to jasná známka, že se začíná dít něco velkého. Špatné, že to ještě pár let potrvá a protože AMD celkem slušně Intel dotáhla, lze předpokládat, že teď bude tak rok-dva klid, kdy obě firmy budou spíše evolučně vylepšovat svoje aktuální architektury. Snad se AMD bude dařit i nadále a i vůči budoucí nové architektuře Intelu bude mít co postavit.

když je v buňce potřeba přepsat jediný bit, znamená to u QLC nutnost „přepsat všech 16 hodnot“Jak často potřebujete přepsat jediný bit na disku bez toho abyste přepsali i hromadu bitů sousedních? Obzvlášť dnes, kdy jsou programovací jazyky a v nich psané frameworky tak vysoko, že se z nich dá tak maximálně spadnout dolů do sémantické mezery a cestou dolu si nabít kokos. Řekl bych, že je velmi nepravděpodobné, že nebude s bitem přepsán celý byte, nebo dva (minimalni velikost integeru v C). Reálně se přepisuje spíš víc. Nemluvě o tom, že SSD mají erease block, který je ještě mnohem větší, takže se už dnes kvůli hypotetické změně bitu přepíše mnohem víc než 15 sousedních bitů (tisíce). Samozřejmě že přístup "narvat co nejvíc informace do jedný buňky" spolehlivosti těhle médií nepřidá. Jen to vaše vysvětlení podle mě trochu pokulhává. Na druhou stranu by to mohli kompenzovat tím, že by zvyšovali rozsah napětí, kterých může buňka nabývat.

Nemluvě o tom, že SSD mají erease block, který je ještě mnohem větší, takže se už dnes kvůli hypotetické změně bitu přepíše mnohem víc než 15 sousedních bitů (tisíce).

To sice ano, ale pokud se jedná o změnu 1 -> 0, u NOR flash a SLC NAND flash se prostě změní jeden bit. Mazání bloku je nutné pouze při změně 0 -> 1.

Samozřejmě že přístup "narvat co nejvíc informace do jedný buňky" spolehlivosti těhle médií nepřidá. Jen to vaše vysvětlení podle mě trochu pokulhává. Na druhou stranu by to mohli kompenzovat tím, že by zvyšovali rozsah napětí, kterých může buňka nabývat.

To není možné z důvodu zmenšování struktur. Pokud budeme pro jednoduchost uvažovat pouze planární MOS strukturu, se snižováním rozměrů musí docházet i ke snižování tloušťky hradlového oxidu a tedy i ke snižování napájecího/pracovního napětí. A samozřejmě i maximální množství náboje, které je možné nahromadit na plovoucím hradle je u menších struktur nižší.

ISSN 1214-1267, (c) 1999-2007 Stickfish s.r.o.