Richard Hughes oznámil, že po společnostech Red Hat a Framework a organizacích OSFF a Linux Foundation, službu Linux Vendor Firmware Service (LVFS) umožňující aktualizovat firmware zařízení na počítačích s Linuxem, nově sponzorují také společnosti Dell a Lenovo. Do dnešního dne bylo díky LVFS provedeno více než 145 milionů aktualizací firmwarů od více než 100 různých výrobců na milionech linuxových zařízení.

Americké technologické společnosti Microsoft, Google a xAI souhlasily, že vládě Spojených států poskytnou přístup k novým modelům umělé inteligence (AI) před jejich uvedením na trh. Oznámila to americká vláda, která tak bude moci prověřit, zda modely nepředstavují hrozbu pro národní bezpečnost. Oznámení podtrhuje rostoucí obavy Washingtonu z rizik spojených s výkonnými AI systémy. Americké úřady chtějí v rámci předběžného přístupu

… více »Společnost Valve zveřejnila (GitLab) nákresy ovladače Steam Controller a puku. Pro všechny, kdo by jej chtěli hacknout nebo modifikovat, případně pro ně navrhnout nějaké příslušenství. Pod licencí Creative Commons (CC BY-NC-SA 4.0).

PHP bylo dlouho distribuováno pod vlastní licencí – s výjimkou částí spadajících pod licenci Zend Engine. Po několikaleté práci se povedlo PHP přelicencovat na 3bodovou licenci BSD.

Na čem pracují vývojáři webového prohlížeče Ladybird (GitHub)? Byl publikován přehled vývoje za duben (YouTube). Na Linuxu je vedle Qt frontendu nově k dispozici také GTK4 / libadwaita frontend.

Neziskové průmyslové konsorcium Khronos Group vydalo verzi 3.1 specifikace OpenCL (Open Computing Language). OpenCL je průmyslový standard pro paralelní programování heterogenních počítačových systémů.

Homebridge pro integraci chytrých domácích zařízení byl vydán ve verzi 2.0.0. Nově vedle protokolu HomeKit Accessory Protocol (HAP) podporuje standard chytré domácnosti Matter.

Omarchy je linuxová distribuce s dlaždicovým správcem oken Hyprland. Založena je na Arch Linuxu. Vydána byla v nové verzi 3.7.0 - The Gaming Edition. Z novinek lze vypíchnout příkaz omarchy a celou řadu herních možností.

CyberChef byl vydán v nové major verzi 11. Přehled novinek v Changelogu. CyberChef je webová aplikace pro analýzu dat a jejich kódování a dekódování, šifrování a dešifrování, kompresi a dekompresi, atd. Často je využívaná při kybernetických cvičeních a CTF (Capture the Flag).

Byla vydána nová verze 2.4.67 svobodného multiplatformního webového serveru Apache (httpd). Řešeno je mimo jiné 11 zranitelností.

První díl seriálu o programovatelné logice. Jedná se zatím o obecný úvod do programovatelných logických obvodů založený na krátkém článku, který jsem poprvé publikoval před více než deseti lety. Oproti původnímu článku je tento text aktualizován a rozšířen. V celém seriálu budu u čtenáře předpokládat základní znalosti elektroniky, Booleovy algebry, logických funkcí a běžných prvků číslicové techniky.

Programovatelné číslicové součástky jsou velmi důležité prvky současné elektroniky. Tyto obvody umožňují implementaci uživatelem definovaných logických funkcí podobně jako třeba zákaznické integrované obvody ASIC, ale s mnohem nižšími náklady na vývoj. Programovatelné logické obvody nejsou žádnou novinkou poslední doby. Za první programovatelné číslicové prvky je možné považovat paměti PROM, které se začaly objevovat na přelomu šedesátých a sedmdesátých let dvacátého století. Během posledních čtyřiceti let prošly programovatelné logické obvody postupným vývojem tak, že dnešní programovatelná hradlová pole jsou často plnohodnotnou náhradou zákaznických integrovaných obvodů a zároveň jsou společně s procesory na špičce vývoje polovodičových technologií.

Zkratka PLD (Programmable Logic Device) se používá pro souhrnné označení všech typů programovatelných logických obvodů. Podle vnitřní struktury je možné číslicové programovatelné součástky rozdělit do tří nebo čtyř hlavních skupin. Tou nejzákladnější a v tomto kontextu často opomíjenou skupinou PLD jsou paměti typu PROM. Ostatní PLD vznikly postupným vývojem a úpravami struktury právě z PROM. První, nejjednodušší a nejstarší skupinou skutečných PLD jsou obvody označované jako klasické PLD. Rozšířením jejich vlastností vznikly komplexní PLD, obvykle značené CPLD. Zobecněním principů používaných v jednoduchých a komplexních PLD a zavedením nových struktur vznikla poslední skupina tvořená programovatelnými hradlovými poli FPGA.

Když necháme stranou diodová pole, která se používala již od dob elektronek a dala by se považovat za skutečně první programovatelné číslicové obvodové prvky, je první uživatelsky programovatelnou číslicovou součástkou paměť typu PROM (Programmable Read-Only Memory). Paměti tohoto typu realizují po naprogramování sadu kombinačních logických funkcí, kde adresová sběrnice představuje vstupy a datová sběrnice výstupy jednotlivých funkcí.

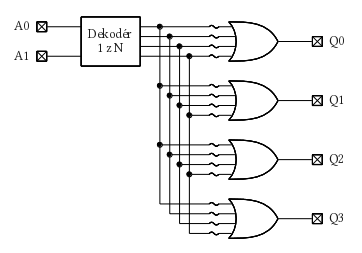

Zjednodušená vnitřní struktura šestnáctibitové PROM se čtyřbitovým slovem je zobrazena na obrázku 1.1. Paměť je tvořena adresovým dekodérem následovaným programovatelnou maticí logických součtů. Adresový dekodér je kombinační logická funkce převádějící binární kód reprezentovaný aktuální adresou na kód 1 z N. Pouze jeden výstup dekodéru může být aktivní. Vlnovky na vstupech jednotlivých součtových hradel představují onen programovatelný prvek. Ten může být v závislosti na naprogramování reprezentován buď propojkou nebo rozpojením.

Obr. 1.1: Vnitřní struktura paměti typu PROM 16b×4

Realizace vlastních programovatelných propojek záleží na konkrétní technologii. Původní bipolární PROM obsahovaly skutečné kovové propojky, které se při programování nevratně přepálily definovaným proudovým impulsem. V CMOS technologiích je propojka realizována jako přenosové hradlo (typicky N-MOS tranzistor) řízený buď plovoucím hradlem (EPROM, EEPROM) nebo jedním bitem konfigurační paměti (SRAM). Programovatelnost pomocí SRAM se ale týká až obvodů FPGA. V PROM a jednoduchých/komplexních PLD se nepoužívá.

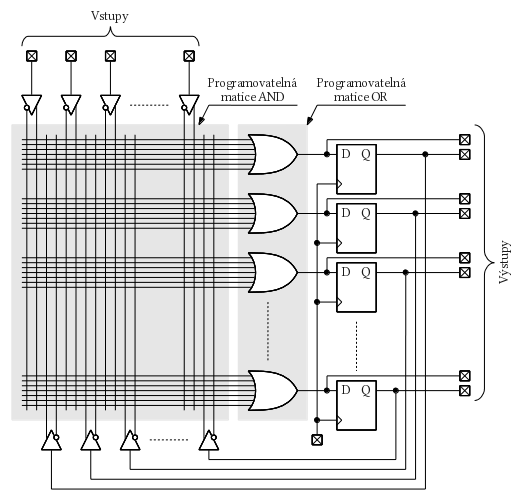

Klasické nebo také jednoduché PLD jsou nejjednodušší programovatelné logické obvody. Typická vnitřní struktura obvodu této kategorie je zobrazena na obrázku 1.2. Struktura vychází z paměti typu PROM, ale zobecňuje ji a rozšiřuje. Pevný adresový dekodér je nahrazen programovatelnou maticí logických součinů a struktura je rozšířena o sekvenční prvky a zpětné vazby.

Obr. 1.2: Vnitřní struktura obvodu typu PAL

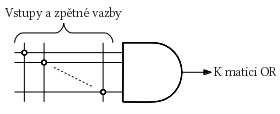

Pro zjednodušení schématu představuje každá vodorovná čára v programovatelné matici logických součinů vždy jedno součinové hradlo. Na vstupy každého hradla lze připojit téměř libovolnou kombinaci vstupních signálů, zpětných vazeb a jejich negací. V závislosti na výrobní technologii konkrétního programovatelného obvodu je ve skutečnosti maximální počet vstupů každého součinového hradla omezen. Principiální zapojení jednoho součinového hradla je znázorněno na obrázku 1.3.

Obr. 1.3: Součinové hradlo obvodu PAL

Kružnice na spojích vodičů obrázku 1.3 představují programovatelné spínače realizované podobně jako v PROM.

Počet vstupů do jednotlivých součtových hradel v matici OR je opět ve skutečnosti omezen a není možné realizovat funkci libovolného počtu vstupů. Programovatelnost matice OR není na schématu 2 vyznačena, ale bude realizována stejně jako u PROM na obrázku 1.1.

Jednotlivé obvody z kategorie klasických PLD se liší přítomností a programovatelností jednotlivých bloků obecné struktury podle obrázku 1.2. Obvody typu PLA (Programmable Logic Array) mají programovatelné obě matice. Výstupní registry byly přítomny v některých novějších obvodech. Dnes se obvody tohoto typu již nevyrábí. Obvody typu PAL (Programmable Array Logic) mají programovatelnou pouze matici logických součinů, zatímco matice logických součtů je pevná. Nejstarší typy se vyráběly bez výstupních registrů, poté začali výrobci přidávat výstupní registry JK, které byly postupně nahrazeny registry typu D. Zástupci kategorie PAL jsou součástky řad PAL, GAL, PEEL a PALCE. Některé typy se dosud vyrábějí a používají.

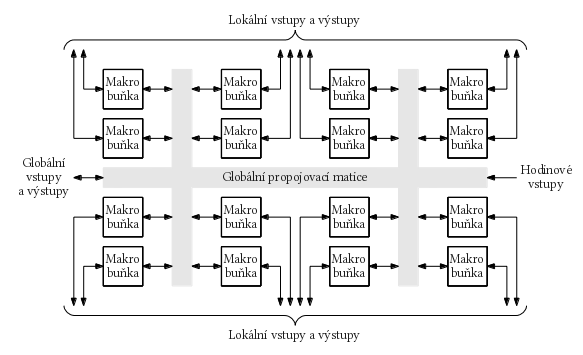

Přestože mohou být klasické PLD velmi univerzální obvodové prvky, složitost implementovatelných funkcí je velmi omezená. Logickým krokem výrobců PLD vedoucím k navýšení množství dostupných prostředků bylo sdružení více jednoduchých PLD struktur na jeden čip spolu s nutnými prostředky pro jejich vzájemné propojení. Takovéto obvody se obvykle označují jako CPLD (Complex Programmable Logic Device). Zjednodušená typická struktura obvodu CPLD je znázorněna na obrázku 1.4.

Obr. 1.4: Struktura obvodu typu CPLD

Jednotlivé makrobuňky (macrocells) CPLD jsou realizovány jako jako struktura PAL nebo PLA. Velikost obvodu CPLD se vyjadřuje počtem makrobuněk a počtem vstupů a výstupů jednotlivých makrobuněk. Konkrétní provedení a velikost jednotlivých makrobuněk se u jednotlivých výrobců obvykle liší, ale základní princip zůstává zachován.

Někteří výrobci programovatelné logiky již klasickou strukturu CPLD opustili a pod označením CPLD prodávají obvody s obecnější vnitřní strukturou blízkou FPGA. Od FPGA se tyto moderní CPLD odlišují obvykle velikostí (jsou výrazně menší), chybějícími speciálními funkčními bloky, menším množstvím globálních prvků a nižší maximální frekvencí hodinových signálů.

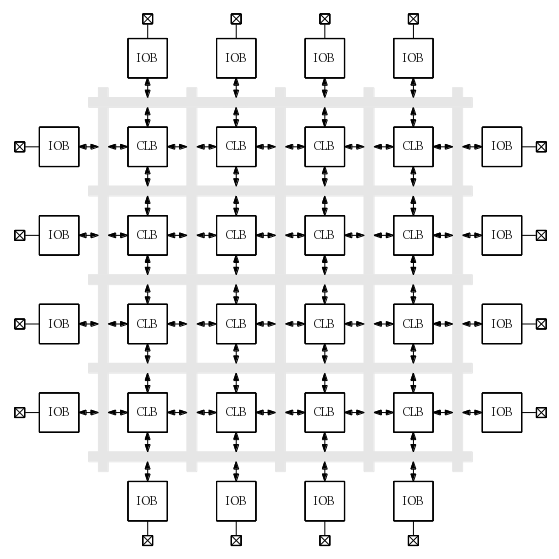

Obvody označované jako FPGA (Field Programmable Gate Array) mají ze všech uživatelem programovatelných obvodů nejobecnější strukturu a zároveň obvykle obsahují největší množství využitelných logických prostředků. Obrázek 1.5 znázorňuje velmi zjednodušenou typickou strukturu charakteristickou pro obvodu typu FPGA.

Obr. 1.5: Zjednodušená struktura obvodu typu FPGA

Obvod FPGA se skládá z bloků vlastní programovatelné logiky CLB (configurable logic blocks), vstupně-výstupních buněk IOB (input-output blocks), programovatelné propojovací matice a konfiguračních prostředků řídících konkrétní nastavení jednotlivých bloků a jejich vzájemné propojení. Jednotliví výrobci navíc přidávají do FPGA další funkční bloky rozšiřující možnosti jejich obvodů. Dnešní typická programovatelná hradlová pole obsahují synchronní blokové paměti, bloky pro správu hodinových signálů založené na PLL nebo DLL, rychlá sériová vstupně-výstupní rozhraní, bloky pro realizaci aritmetických operací, mikroprocesory, paměťové řadiče a podobně.

Programovatelná hradlová pole jsou nejvýznamnější skupinou programovatelných logických obvodů. Jsou to nejuniverzálnější programovatelné logické obvody s nejobecnější vnitřní strukturou, ale také z hlediska pochopení a použití jsou nejsložitější. Popisu FPGA bude věnována celá následující část.

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()

http://cs.wikipedia.org/wiki/Programovateln%C3%BD_logick%C3%BD_automat, https://www.google.cz/search?hl=cs&q=PLC+siemens&bav=on.2,or.r_gc.r_pw.r_cp.r_qf.&bpcl=40096503&biw=1745&bih=970&um=1&ie=UTF-8&tbm=isch&source=og&sa=N&tab=wi&ei=86DRULGtL4TStQbFyYGIBQ To kdyby někdo sestrojil na linuxu by byl borec a vydělal by jsi kupu prachů!

http://cs.wikipedia.org/wiki/Programovateln%C3%BD_logick%C3%BD_automat, https://www.google.cz/search?hl=cs&q=PLC+siemens&bav=on.2,or.r_gc.r_pw.r_cp.r_qf.&bpcl=40096503&biw=1745&bih=970&um=1&ie=UTF-8&tbm=isch&source=og&sa=N&tab=wi&ei=86DRULGtL4TStQbFyYGIBQ To kdyby někdo sestrojil na linuxu by byl borec a vydělal by jsi kupu prachů!

Ve škole jsme se hráli s tecomatyNesmíš zanevřít na celou jednu architekturu jen kvůli hloupýmu Mosaicu

. Já jsem v něm dělal semestrální práci ve vmware na duronu 666MHz

. Já jsem v něm dělal semestrální práci ve vmware na duronu 666MHz  . A i přesto mě zásobníky nevaděj (nejak extra

. A i přesto mě zásobníky nevaděj (nejak extra  ).

).

Bavilo me to cist, jen tak dal!

Bavilo me to cist, jen tak dal!

Teoreticky to sice jde i v PLD bez registrů pomocí vnějších zpětných vazeb, ale není to typická ani doporučená aplikace.I prakticky, ring oscilátor v GALu je toho důkazem

. Jinak ještě dodám, že se ty déčka můžou použít i jako posuvný registr nebo paměťový prvek (to spíš u CPLD a vejš).

. Jinak ještě dodám, že se ty déčka můžou použít i jako posuvný registr nebo paměťový prvek (to spíš u CPLD a vejš).

A malé rýpnutí : ještě před diodovými poli se takovéhle záležitosti realizovaly mechanicky pomocí různých hřebenů a válečků. Typickými představiteli byly automatické "programovatelné" stavy nebo flašinet, ale i mechanické počítací stroje, např Ascota z bývalé NDR (odkaz jsem kupodivu žádný nenašel a přitom to není až tak dávná historie)...

A malé rýpnutí : ještě před diodovými poli se takovéhle záležitosti realizovaly mechanicky pomocí různých hřebenů a válečků. Typickými představiteli byly automatické "programovatelné" stavy nebo flašinet, ale i mechanické počítací stroje, např Ascota z bývalé NDR (odkaz jsem kupodivu žádný nenašel a přitom to není až tak dávná historie)...

Teď ještě jak se s tím dělá/jak se to programuje.GALBlasterem. Pokud to nemá být obsah dalšího dílu, tak někde vyhrabu linky.

ještě před diodovými poli se takovéhle záležitosti realizovaly mechanicky pomocí různých hřebenů a válečků.Tohle už bylo ve století páry

.

.