CiviCRM (Wikipedie) bylo vydáno v nové verzi 6.14.0. Podrobnosti o nových funkcích a opravách najdete na release stránce. CiviCRM je robustní open-source CRM systém navržený speciálně pro neziskové organizace, spolky a občanské iniciativy. Projekt je napsán v jazyce PHP a licencován pod GNU Affero General Public License (AGPLv3). Český překlad má nyní 45 % přeložených řetězců a přibližuje se milníku 50 %. Potřebujeme vaši pomoc, abychom se dostali dál. Pokud máte chuť přispět překladem nebo korekturou, přidejte se na platformu Transifex.

Další lokální zranitelností Linuxu je ssh-keysign-pwn. Uživatel si může přečíst obsah souborů, ke kterým má právo ke čtení pouze root, například soubory s SSH klíči nebo /etc/shadow. V upstreamu již opraveno [oss-security mailing list].

Singularity (YouTube) je nejnovější otevřený film od Blender Studia. Jedná se o jejich první 4K HDR film.

Vyšla hra Život Není Krásný: Poslední Exekuce (Steam, ProtonDB). Kreslená point & click adventura ze staré školy plná černého humoru a nekorektního násilí. Vžijte se do role zpustlého exekutora Vladimíra Brehowského a projděte s ním jeho poslední pracovní den. Hra volně navazuje na sérii Život Není Krásný.

Společnost Red Hat představila Fedora Hummingbird, tj. linuxovou distribuci s nativním kontejnerovým designem určenou pro vývojáře využívající AI agenty.

Hru The Legend of Zelda: Twilight Princess od společnosti Nintendo si lze nově díky projektu Dusklight (původně Dusk) a reverznímu inženýrství zahrát i na počítačích a mobilních zařízeních. Vyžadována je kopie původní hry (textury, modely, hudba, zvukové efekty, …). Ukázka na YouTube. Projekt byl zahájen v srpnu 2020.

Byla vydána nová major verze 29.0 programovacího jazyka Erlang (Wikipedie) a související platformy OTP (Open Telecom Platform, Wikipedie). Detailní přehled novinek na GitHubu.

Po zranitelnostech Copy Fail a Dirty Frag přichází zranitelnost Fragnesia. Další lokální eskalace práv na Linuxu. Zatím v upstreamu neopravena. Přiřazeno ji bylo CVE-2026-46300.

Sovereign Tech Agency (Wikipedie) prostřednictvím svého fondu Sovereign Tech Fund podpoří KDE částkou 1 285 200 eur.

Google na včerejší akci The Android Show | I/O Edition 2026 (YouTube) představil celou řadu novinek: Gemini Intelligence, notebooky Googlebook, novou generaci Android Auto, …

Po delší odmlce konečně další pokračování seriálu o programovatelné logice. Tentokrát se jedná o úvod do vývojových prostředků pro programovatelné logické obvody. Informace nejsou kompletní, protože tato kapitola je poměrně dlouhá a bude dokončena až v příštím pokračování. Text opět navazuje na předchozí dva díly, které najdete zde a zde.

Programovatelné logické obvody se sebelepší vnitřní architekturou by nebyly prakticky použitelné bez odpovídající podpory vývojových prostředků. Teoreticky je při znalosti vnitřní architektury konkrétního PLD možné přímo vytvořit finální schéma propojení jednotlivých funkčních bloků. U jednoduchých PLD jako jsou obvody PAL nebo GAL je něco takového i prakticky realizovatelné, ale u dnešních složitých FPGA je to něco naprosto nereálného.

Základní vývojové prostředky pro programovatelnou logiku musí zajistit transformaci vstupního návrhu nebo popisu funkce do výstupního formátu použitelného pro konfiguraci nebo naprogramování konkrétní součástky. Ve skutečnosti je to pouze jedna z mnoha funkcí dnešních vývojových prostředků používaných pro aplikaci programovatelné logiky. Vývojová prostředí pro FPGA se stávají neustále složitější a komplexnější. Jsou často podobná velkým vývojovým systémů pro digitální integrované obvody a mnohé používané nástroje jsou totožné. Typické vývojové prostředky pro programovatelnou logiku je možné rozdělit do několika základních skupin podle jejich funkce:

Implementace

Verifikace

Hardware

Implementační nástroje slouží pro převod návrhu funkce do výstupního formátu použitelného pro fyzickou konfiguraci programovatelné součástky. Do této skupiny patří nástroje pro syntézu a implementaci.

Verifikační nástroje slouží pro ověření funkce jak samotného návrhu, tak i jednotlivých mezivýsledků implementačního procesu. Do této skupiny patří číslicové nebo smíšené simulátory a různé analytické nástroje. Může se jednat o nástroje pro statickou časovou analýzu (STA) nebo třeba analyzátory výstupů implementačních prostředků.

Hardwarové prostředky slouží především pro verifikaci, ověření funkce výsledného obvodu a pro jeho charakterizaci. Jedná se například o různé vývojové a testovací desky, programátory, programovací adaptéry a JTAG adaptéry pro konfiguraci, měření, testování a ladění. Používají se často pro ověření funkce a charakterizaci před finálním návrhem vlastní desky plošných spojů. Některé z hardwarových prostředků slouží k produkčnímu programování PLD nebo jejich konfiguračních pamětí.

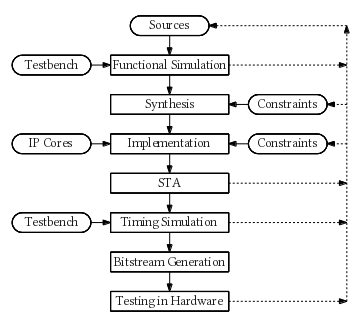

Schéma typického postupu vývoje pro programovatelné logické obvody je znázorněno vývojovým diagramem na obrázku 2.1. Jedná se o zjednodušený postup vycházející z postupu vývoje číslicových integrovaných obvodů.

Obr. 2.1: Postup vývoje pro FPGA

V diagramu na obrázku 2.1 jsou použity anglické výrazy, protože některé z nich nemají české ekvivalenty. Význam jednotlivých bloků diagramu je popsán dále.

Sources

Soubor vstupních dat, která popisují předpokládanou funkci výsledného obvodu. Může se jednat o kombinaci textových souborů v různých jazycích, obvodových a blokových schémat, stavových diagramů a podobně.

Testbench

Pomocné soubory pro simulace a verifikace. Obvykle se jedná o popis generování testovacích vektorů a vyhodnocování výsledků testů ve vhodném jazyce. Součástí bývají také simulační modely použitých IP jader a externích součástek.

IP Cores

Hotové funkční bloky využité v návrhu. Může se jednat o zakoupená jádra nebo vlastní univerzální moduly připravené pro znovuvyužití v mnoha různých projektech. Jádra jsou pro implementaci použita ve formě netlistů nebo jiných formátů přímo podporovaných implementačními nástroji.

Constraints

Jedná se o soubory popisující různé omezující podmínky, kterými se nástroje pro syntézu a implementaci musí řídit. Typicky jde o fyzické vlastnosti vstupně-výstupních signálů jako je přiřazení pinů na pouzdře součástky, nastavení elektrických vlastností budičů a přijímačů a podobně. Další skupinou jsou omezení týkající se umístění a propojení funkčních bloků na čipu programovatelné součástky. Poslední důležitá skupina omezujících podmínek řídí časové poměry v obvodu jako je například nastavení hodinových frekvencí, povolené zpoždění průchodu signálu a podobně.

Functional Simulation

Funkční simulace je pro programovatelnou logiku nejdůležitější verifikační krok. Měla by ověřit funkční správnost návrhu. Pokud je návrh v pořádku, je možné pokročit k dalšímu bodu, jinak je třeba návrh upravit tak, aby funkční požadavky ověřované simulací splnil.

Synthesis

Syntéza je prvním krokem vlastní konverze vstupního popisu funkce do formátu použitelného pro konfiguraci programovatelné součástky. Výstupem syntézy je takzvaný netlist, což je v podstatě schéma popsané textovým nebo binárním formátem. Netlist obsahuje již funkční bloky cílové technologie, jako jsou například LUT, registry, budiče, a kombinuje je navzájem seznamem jednotlivých spojů.

Implementation

Implementace slouží pro správné umístění netlistu do konkrétního programovatelného obvodu. Skládá se z několika kroků, jejichž výsledkem je speciální verze netlistu, kde každý blok i každý spoj je jednoznačně umístěn na konkrétní pozici v programovatelné součástce.

STA

Statická časová analýza je důležitý verifikační nástroj. Pokud je návrh správný po funkční stránce, odhalí STA případné problémy s časováním. Důležitou podmínkou je však správná a především kompletní sada fyzických a časových omezujících podmínek – constraints.

Timing Simulation

Časová simulace se při vývoji pro programovatelnou logiku používá velice zřídka. Při této simulaci se místo vstupního popisu funkce používá výstup implementace převedený obvykle do netlistu v simulačním jazyku. Tento netlist obsahuje i kompletní informace o skutečných zpožděních jednotlivých bloků a spojů. Při vývoji pro programovatelnou je za dodržení správných postupů správná funkce výsledku zajištěna již díky funkční simulaci a STA. Programovatelné součástky i implementační nástroje jsou dostatečně charakterizovány od výrobce a funkční správnost společně s ověřením splnění časových požadavků pomocí STA zaručuje správnost výsledku.

Bitstream Generation

Generátor bitstreamu převede výstupní netlist z implementace na soubor, který již přímo řídí nastavení jednotlivých konfiguračních propojek programovatelné součástky. Tento soubor je již přímo použitelný pro fyzické naprogramování nebo konfiguraci PLD.

Testing in Hardware

Posledním krokem verifikace je otestování funkce ve skutečném programovatelném obvodu společně se skutečnými externími součástkami. Součástí testování je obvykle počáteční ověření funkce, měření parametrů a charakterizace. V případě problémů je možné využít různé hardwarové prostředky pro ladění.

Do procesu návrhu programovatelných logických obvodů vstupuje mnoho různých dat, sloužících pro popis funkce, pomocná data a skripty pro simulace a verifikace, pomocná data a skripty pro implementaci a další.

Požadovaná výsledná funkce programovatelného obvodu může být popsána kombinací několika následujících základních metod:

Popis pomocí některého jazyka pro popis hardware – HDL (Hardware Description Language)

Popis pomocí podporovaného vysokoúrovňového jazyka – HLL (High-Level Language)

Blokové schéma zapojení, kde jednotlivé bloky jsou vnitřně realizovány libovolnou jinou metodou

Obvodové schéma zapojení využívající připravené knihovny základních primitiv i funkčních bloků na vyšší úrovni

Další podporované formy grafického popisu jako například stavové nebo vývojové diagramy, vysokoúrovňové diagramy MATLAB/Simulink a podobně

IP jádra ve formě netlistu nebo pevného makra

Další speciální soubory jako například definice procesorových subsystémů

Nejrozšířenější metodou popisu logických obvodů je v dnešní době použití HDL. Prakticky se pro vstup syntézy používají jazyky VHDL, Verilog a SystemVerilog, což jsou specializované jazyky určené pro popis číslicových systémů od velmi nízké úrovně typu netlist až po vysokoúrovňový popis využívající metod objektově orientovaného programování a dalších vlastností převzatých z moderních programovacích jazyků. Výhodou použití HDL je univerzálnost a přenositelnost, protože jazyky jsou standardizovány organizací IEEE a všechny současné nástroje pro syntézu podporují alespoň VHDL a Verilog.

Použití HLL pro návrh číslicových systémů není dosud příliš rozšířené, ale začínají se objevovat použitelné nástroje. Syntéza z HLL obvykle probíhá ve dvou krocích, kdy je zdrojový popis ve vysokoúrovňovém jazyce nejdříve přeložen do některého HDL a ten je následně předán syntéze. HLL pro popis hardware obvykle vycházejí až na výjimky z jazyka C nebo C++. Zvláštní kategorií jsou nástroje určené pro MATLAB, které převádějí M-kód na HDL.

Obvodová i bloková schémata se v dnešní době používají již velmi zřídka. Současné programovatelné logické obvody poskytují takové množství logických prostředků, že typické návrhy jsou velmi rozsáhlé. Doba vývoje, přehlednost a udržovatelnost komplexních digitálních návrhů ve formě schémat jsou mnohem horší ve srovnání s HDL.

Ostatní formy popisu jsou většinou specifické pro konkrétního výrobce nebo určité nástroje. Společnou typickou vlastností je, že se vždy před syntézou vygeneruje syntetizovatelný popis v HDL.

Kromě popisu funkce obvodu potřebuje simulátor ještě další podpůrné soubory. Jde jednak o soubory generující vstupní hodnoty a vyhodnocující výstupy, které tvoří takzvaný testbench, a dále o pomocné skripty řídící vlastní proces simulace, jeho automatizaci a podobně.

Testbenche se v dnešní době realizují buď v HDL nebo HVL (Hardware Verification Language). Speciální a vysokoúrovňové jazykové konstrukce vhodné pro simulace a verifikace nabízí z HDL především VHDL, SystemVerilog a SystemC. Nejpoužívanější HVL jsou PSL (Property Specification Language), e, OpenVera a opět SytemVerilog a SystemC, což jsou jazyky kombinující vlastnosti HDL a HVL. Důležitými vstupy pro časové simulace jsou soubory SDF (Standard Delay Format), které definují zpoždění jednotlivých prvků.

Simulace funkčního popisu zapsaného v HLL se obvykle provádí ve stejném jazyce. Samozřejmě je ale možné převést popis z HLL do HDL a výsledek poté simulovat v běžném digitálním simulátoru s pomocí HDL/HVL testbenchů.

Součástí vstupních souborů pro simulace a verifikace bývají často skripty pro řízení vlastních simulačních programů. Tyto pomocné soubory obvykle zajistí vytvoření potřebných knihoven, kompilaci funkčního popisu ve správném pořadí do správných knihoven, nastavení simulátoru, zobrazení požadovaných výstupů a spuštění simulace.

Implementační nástroje potřebují kromě popisu funkce ještě další vstupní data, která ovlivňují výsledek implementačního procesu. Jedná se především o definici jednotlivých fyzických omezujících podmínek, tzv. constraints. Je nutné jednotlivým vstupně-výstupním signálům přiřadit konkrétní piny programovatelné součástky a nastavit elektrické parametry vstupních přijímačů a výstupních budičů. Další parametry, které mají vliv na implementaci jsou časové vlastnosti hodinových signálů, datových vstupů a výstupů, stejně jako některých interních signálů. Důležité je například správně ošetřit přechody mezi asynchronními hodinovými signály nebo delší kombinační logické cesty. Poslední oblastí je možnost ručního umístění některých funkčních bloků na čipu FPGA nebo vymezení oblastí, ve kterých smí být daný blok automaticky umístěn. Jedná se o takzvaný floorplannig.

Další skupinou vstupů pro implementační proces je správné nastavení implementačních nástrojů. To je obvykle možné dělat interaktivně v GUI, pomocí konfiguračních souborů, nebo implementačních skriptů. Skriptování implementačních nástrojů pro programovatelnou logiku se provádí typicky v jazyce TCL, některé nástroje podporují i Perl.

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()