Richard Hughes oznámil, že po společnostech Red Hat a Framework a organizacích OSFF a Linux Foundation, službu Linux Vendor Firmware Service (LVFS) umožňující aktualizovat firmware zařízení na počítačích s Linuxem, nově sponzorují také společnosti Dell a Lenovo. Do dnešního dne bylo díky LVFS provedeno více než 145 milionů aktualizací firmwarů od více než 100 různých výrobců na milionech linuxových zařízení.

Americké technologické společnosti Microsoft, Google a xAI souhlasily, že vládě Spojených států poskytnou přístup k novým modelům umělé inteligence (AI) před jejich uvedením na trh. Oznámila to americká vláda, která tak bude moci prověřit, zda modely nepředstavují hrozbu pro národní bezpečnost. Oznámení podtrhuje rostoucí obavy Washingtonu z rizik spojených s výkonnými AI systémy. Americké úřady chtějí v rámci předběžného přístupu

… více »Společnost Valve zveřejnila (GitLab) nákresy ovladače Steam Controller a puku. Pro všechny, kdo by jej chtěli hacknout nebo modifikovat, případně pro ně navrhnout nějaké příslušenství. Pod licencí Creative Commons (CC BY-NC-SA 4.0).

PHP bylo dlouho distribuováno pod vlastní licencí – s výjimkou částí spadajících pod licenci Zend Engine. Po několikaleté práci se povedlo PHP přelicencovat na 3bodovou licenci BSD.

Na čem pracují vývojáři webového prohlížeče Ladybird (GitHub)? Byl publikován přehled vývoje za duben (YouTube). Na Linuxu je vedle Qt frontendu nově k dispozici také GTK4 / libadwaita frontend.

Neziskové průmyslové konsorcium Khronos Group vydalo verzi 3.1 specifikace OpenCL (Open Computing Language). OpenCL je průmyslový standard pro paralelní programování heterogenních počítačových systémů.

Homebridge pro integraci chytrých domácích zařízení byl vydán ve verzi 2.0.0. Nově vedle protokolu HomeKit Accessory Protocol (HAP) podporuje standard chytré domácnosti Matter.

Omarchy je linuxová distribuce s dlaždicovým správcem oken Hyprland. Založena je na Arch Linuxu. Vydána byla v nové verzi 3.7.0 - The Gaming Edition. Z novinek lze vypíchnout příkaz omarchy a celou řadu herních možností.

CyberChef byl vydán v nové major verzi 11. Přehled novinek v Changelogu. CyberChef je webová aplikace pro analýzu dat a jejich kódování a dekódování, šifrování a dešifrování, kompresi a dekompresi, atd. Často je využívaná při kybernetických cvičeních a CTF (Capture the Flag).

Byla vydána nová verze 2.4.67 svobodného multiplatformního webového serveru Apache (httpd). Řešeno je mimo jiné 11 zranitelností.

Druhé pokračování seriálu o programovatelné logice. Tato část popisuje typickou strukturu programovatelných hradlových polí (FPGA). Číslování kapitol plynule navazuje na minulý díl.

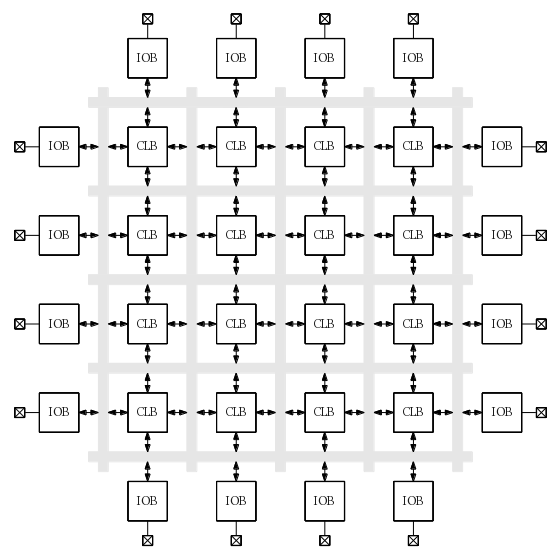

Velice zjednodušená principiální struktura programovatelného hradlového pole na obrázku 1.5 vystihuje základní a nejdůležitější vlastnost FPGA, která je odlišuje od jejich předchůdců. Programovatelná hradlová pole jsou tvořena velkým množstvím menších konfigurovatelných bloků obecné logiky, které jsou navzájem propojitelné propojovací maticí. Komunikaci s okolním prostředím zajišťují vstupně-výstupní bloky. Kromě logických bloků, vstupně-výstupních bloků a propojovací matice obsahují FPGA ještě další speciální funkční bloky, které se u jednodušších PLD nepoužívaly. Jedná se například o bloky statických pamětí RAM, správy hodinových signálů, speciální vstupně-výstupní bloky a podobně.

Obr. 1.5: Zjednodušená struktura obvodu typu FPGA

Následující text nepopisuje žádné konkrétní FPGA, ale pouze obecné vlastnosti typické pro FPGA různých výrobců. Použité názvosloví je často převzato z terminologie používané firmou Xilinx, ale občas se v textu vyskytnou i výrazy pocházející od firmy Altera. Obvody obou hlavních světových výrobců FPGA sice vycházejí ze stejných obecných principů, ale konkrétní provedení a používaná terminologie se liší. Pro seznámení se se skutečnou realizací programovatelných hradlových polí je třeba prostudovat dokumentaci konkrétních produktů jednotlivých výrobců. Tato kapitola by měla pomoci lepšímu porozumění firemní dokumentaci.

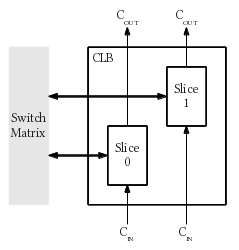

Konfigurovatelné logické bloky jsou základním stavebním prvkem FPGA. Jedná se o bloky umožňující realizaci kombinačních i sekvenčních logických funkcí několika jednotek až desítek binárních vstupů s několika výstupy. Firma Xilinx označuje tyto základní bloky Configurable Logic Blocks (CLB), Altera používá označení Logic Array Blocks (LAB). Vzájemné propojení jednotlivých konfigurovatelných logických bloků zajišťuje programovatelná propojovací matice.

Obr. 1.6: Konfigurovatelný logický blok

Konfigurovatelné logické bloky jsou obvykle realizovány jako kombinace dvou menších bloků označovaných jako logické řezy jak je znázorněno na obrázku 1.6. Název vychází z názvosloví firmy Xilinx — Slices, zatímco Altera nazývá tyto elementární bloky Adaptive Logic Modules (ALM). Zjednodušené obecné schéma jednoho řezu je na obrázku 1.7. Skutečná realizace elementárního bloku logiky je v dnešních FPGA mnohem složitější a řezy obvykle obsahují dvojnásobné množství základních logických prvků. Zjednodušené schéma je lepší pro pochopení základní struktury.

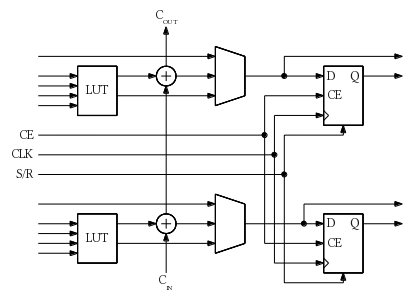

Obr. 1.7: Obecný logický řez

Typický logický řez se skládá ze čtyř vzájemně se doplňujících částí:

Programovatelná logická tabulka LUT (look-up table) slouží k realizaci libovolné kombinační logické funkce. Jedná se v podstatě o paměť typu RAM, jejíž obsah je při běžném použití pevně dán konfiguračními daty. Realizuje tedy jednu nebo dvě binární funkce několika (typicky čtyř, pěti nebo šesti) vstupních binárních proměnných. Kromě této základní funkce umožňují LUT obvykle realizaci i jiných typů funkčních bloků jako jsou malé paměti RAM a ROM, nebo posuvné registry.

Řetězec rychlého šíření přenosu (carry chain) umožňuje vytvoření různých aritmetických obvodů, jako jsou například sčítačky. Zatímco běžné vstupy a výstupy logických řezů jsou připojeny k pomalé globální propojovací matici, vstup a výstup přenosu CIN a COUT jsou přímo propojeny se sousedními konfigurovatelnými logickými bloky ve stejném sloupci.

Programovatelné multiplexery umožňují realizaci logických funkcí více proměnných než je šířka jedné LUT. Funkce je pak realizována zkombinováním výstupů několika LUT v jednom logickém řezu pomocí multiplexerů. Obdobné funkcionality je sice možné dosáhnout kombinací několika logických bloků, ale propojení mezi jednotlivými CLB je mnohem pomalejší než přímý spoj mezi LUT a multiplexery. Zjednodušené schéma na obrázku 1.7 neobsahuje multiplexer umožňující toto využití logického řezu, protože by schéma bylo nepřehledné. Tento přidaný multiplexer by byl umístěn mezi stávajícími dvěma multiplexery na schématu a jeho výstup by byl dále různě kombinován s výstupy druhých dvou.

Registry v logických řezech umožňují realizaci sekvenčních logických funkcí. Při konfiguraci řezu je obvykle možné nastavit vlastnosti jednotlivých registrů jako třeba využití clock-enable, polarita a typ set/reset vstupu a podobně. Speciální vstupy pro registry na obrázku 1.7 jsou obvykle sdíleny všemi registry v rámci jednoho konfigurovatelného logického bloku nebo alespoň v rámci řezu. To znamená, že všechny registry musí používat stejný hodinový signál, clock-enable, i reset. Ne každý registr však musí clock-enable a reset používat, případně může reset využívat jiným způsobem než ostatní registry.

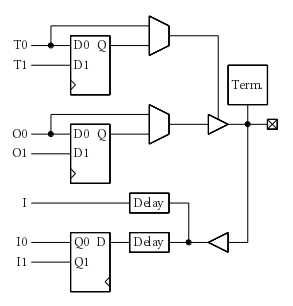

Vstupně-výstupní bloky (IOB) zprostředkovávají spojení mezi FPGA a vnějším prostředím. Každý vnější signál vstupuje do FPGA prostřednictvím IOB a každý výstupní signál opouští FPGA opět přes IOB. Zjednodušené schéma vstupně-výstupního bloku je na obrázku 1.8.

Obr. 1.8: Vstupně-výstupní blok

Vstupně-výstupní blok obsahuje vstupní a výstupní registry, budiče a přijímače, zpožďovací linky, obvody impedančního přizpůsobení a ochranné obvody. Vstupní i výstupní registry jsou u všech dnešních FPGA realizovány pomocí kombinace dvou registrů tak, aby umožňovaly vstup a výstup DDR signálů. Samozřejmě mohou být nakonfigurovány do běžného režimu SDR.

Výstup signálu je realizován volitelným výstupním registrem následovaným třístavovým budičem. Výstup budiče je přímo připojen na pin FPGA. Třístavový budič je řízen druhou datovou cestou podobnou datové, která opět obsahuje volitelný DDR/SDR registr.

Vstupní externí signál je přiveden na konfigurovatelný přijímač, ve schématu představovaný pouze jednoduchým budičem. Ve skutečnosti se jedná o různé přijímače pro jednotlivé podporované I/O standardy následované multiplexerem. Výstup přijímače může být přes konfigurovatelnou zpožďovací linku přiveden přímo na propojovací matici FPGA nebo na DDR/SDR vstupní registr a z něho teprve na propojovací matici. Pro vstup diferenciálních signálů obsahuje přijímač ještě druhý vstup připojený do sousedního I/O bloku. Programovatelné zpožďovací linky umožňují realizaci časového posunu vstupního signálu. Tím je možné například korigovat vzájemný fázový posun signálů, případně posun signálu vůči hodinám.

Ochranné obvody, které nejsou na zjednodušeném schématu nakresleny, chrání logiku IOB před poškozením z vnějšího světa v důsledku EMI nebo nesprávného použití či zapojení. Obvody impedančního přizpůsobení umožňují přizpůsobit vnitřní impedanci budiče v FPGA impedanci externího vedení nebo zakončit externí vedení správně přizpůsobenou impedancí. Novější FPGA podporují dynamické řízení zakončovací impedance, což je důležité například pro připojení různých variant DDR a QDR rozhraní nebo třeba PCIe.

Vzájemné propojení jednotlivých funkčních bloků FPGA zajišťují různé programovatelné propojovací matice a spoje. Typické hradlové pole obsahuje tři různé typy propojovacích prostředků:

Globální propojovací prostředky jsou nejuniverzálnější a umožňují vzájemné propojení libovolných funkčních bloků FPGA. Jsou realizovány jako několik vrstev různě organizovaných spojů s propojovacími maticemi pro jednotlivé funkční bloky. Vlastní organizace spojů se liší mezi výrobci i mezi jednotlivými produktovými řadami. Často bývají spoje organizovány jako sada horizontálních a vertikálních vodičů různých délek. Programovatelné propojovací matice umožňují připojení vstupů a výstupů funkčních bloků k jednotlivým propojovacím vodičům. Přestože globální propojovací prostředky poskytují nejvíce stupňů volnosti v propojení jednotlivých bloků, mají zase některé nevýhody. Každý globální spoj je poměrně dlouhý vodič s velkým množstvím programovatelných spínačů a tedy velkou kapacitou, což se projeví na rychlosti šíření signálů.

Lokální propojovací prostředky umožňují propojení pouze sousedních funkčních bloků. Jedná se například o propojení řetězců šíření přenosu logických řezů, propojení diferenciálních signálů vstupně-výstupních bloků, ale i krátké rychlé spoje mezi sousedními konfigurovatelnými logickými bloky. Lokální spoje jsou mnohem kratší, s méně spínači a nižší kapacitou než spoje globální. Lokální spoje tedy způsobují mnohem nižší zpoždění signálů než globální spoje.

Speciální propojovací prostředky slouží pro spojení mezi vyhrazenými vstup a výstupy funkčních bloků. Jedná se především pro spoje určené k šíření hodinových signálů a dalších globálních signálů typu reset, tristate apod. Tyto speciální propojovací prostředky jsou optimalizovány tak, aby způsobovaly co nejmenší zpoždění procházejících signálů. Samozřejmě nemohu být použity pro běžné signály, ale pouze pro jeden konkrétní typ signálů. Například hodinové spoje mohou být připojeny pouze k vyhrazeným hodinovým vstupům a výstupům jednotlivých funkčních bloků, ale už ne k ostatním běžným portům. Množství speciálních propojovacích prostředků v FPGA je obvykle velmi omezené a často bývají realizovány ve dvou různých provedeních jako globální a lokální podobně jako běžné signálové spoje.

Dnešní programovatelná hradlová pole obsahují další, často jednoúčelové, funkční bloky usnadňující použití FPGA. Typickými zástupci této kategorie jsou blokové paměti, násobičky a jiné aritmetické obvody, obvody pro správu a generování hodinových signálů, sériové transceivery a další.

Blokové paměti jsou obvykle dvouportové statické paměti RAM o kapacitě jednotek až desítek kilobytů a s konfigurovatelnou šířkou adresových a datových sběrnic. Takovýto paměťový blok je vysoce univerzální. Může být použit jako jednoportová i dvouportová paměť typu RAM i ROM. Datové sběrnice mohou být obvykle nastaveny na šířku 1, 2, 4, 8/9, 16/18, 32/36, nebo 64/72 bitů. Čísla za lomítkem představují varianty s paritními bity. Dvouportové blokové paměti usnadňují realizaci různých typů speciálních pamětí jako jsou FIFO, kruhové buffery, CAM apod.

Aritmetické obvody jsou reprezentovány obvykle celočíselnými násobičkami, případně složitějšími DSP bloky umožňujícími realizaci náročnějších matematických operací v jednom hodinovém cyklu. Typickým příkladem jednodušších, ale nejčastějších operací realizovaných pomocí DSP bloků je MAC (Multiply-and-Accummulate), což je základní operace číslicové filtrace a téměř všech DSP algoritmů.

Bloky pro správu a generování hodinových signálů jsou založeny na PLL (phase-locked loop — fázový závěs) nebo DLL (delay-locked loop). Složitější hodinové bloky ve větších FPGA často obsahují i několik PLL a DLL. Tyto bloky nabízejí funkce jako je syntéza a dělení hodinových signálů, generování fázově posunutých hodin, kompenzace vnitřních i vnějších zpoždění a fázových posunů a podobně. Vstupy a výstupy těchto bloků jsou obvykle připojený přímo ke speciálním spojům určeným pro šíření hodinových signálů. Na rozdíl od předchozích dvou typů speciálních funkčních bloků nejdou hodinové obvody jednoduše nahradit běžnou logikou FPGA.

Sériové transceivery umožňují poměrně jednoduchou realizaci velmi rychlých sériových rozhraní. Blok transceiveru obvykle obsahuje diferenciální budič a přijímač, serializer a deserializer, kodér a dekodér, extraktor hodinového signálu a další pomocné obvody. Pomocí transceiverů je možné sériově komunikovat s okolím rychlostmi v řádech jednotek až desítek gigabitů za sekundu. Interní rozhraní v FPGA je pak realizováno synchronními paralelními daty s mnohem nižší hodinovou frekvencí. Sériové transceivery jsou nezbytné pro realizaci mnoha standardních sériových rozhraní jako jsou například PCIe, XAUI pro 10Gbps Ethernet a mnohá další.

Z ostatních funkčních bloků, které se vyskytují v FPGA si zaslouží zmínku řadiče pamětí a mikroprocesory. Některá hradlová pole obsahují hotový řadič dynamických pamětí, který obvykle podporuje paměti typu SDR, DDR, DDR2 a DDR3 SDRAM. Hotový blok řadiče uspoří mnoho logických prostředků a často významně zvýší datovou propustnost externí dynamické paměti oproti realizaci řadiče pomocí běžné logiky. Zabudovávání mikroprocesorů do FPGA není žádná novinka posledních let. Některé starší high-end FPGA obsahovaly mikroprocesor PowerPC řady 4xx nebo ARM s instrukční sadou verze 2. Po několikaleté přestávce se výrobci k této možnosti začali navracet a na trhu se objevují nová FPGA s vestavěnými vícejádrovými procesory ARM Cortex-A9. Tvoří tak zajímavou alternativu běžným SoC svou programovatelností, ale i FPGA díky mnohem výkonnějšímu CPU než běžné soft-core procesory.

Jak již bylo zmíněno na začátku této kapitoly, jedná se o zjednodušený popis neexistujícího obecného programovatelného hradlového pole. Struktura skutečných FPGA je do detailu popsána ve firemní dokumentaci jednotlivých obvodů. Dokumentaci hledejte na webech výrobců programovatelné logiky:

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()

.

.

BASH

Netvrdím, že vytvořit open-source PLC na úrovni současných komerčních je nereálné, ale není to až tak daleko od pravdy. Jenom náklady na vývoj hardware, firmware pro PLC a vývojové prostředí pro PC budou obrovské. Nedovedu si dost dobře představit z čeho by se to financovalo.

Všichni výrobci FPGA nabízejí vždy nějakou trochu omezenou verzi svých vývojových prostředí zdarma. Rozhodně bych si nedovolil říci, že podporují pouze malé obvody. V dnešní době to jsou větší a rychlejší FPGA než byl ještě před pár lety high-end.

Vývojovým prostředím se budu věnovat v příští části.

(nebo by to byl hooodně drahej koníček), navíc bys musel vyvíjet opravdu náročnou aplikaci, abys pak využil aspoň nějakou významnou část toho FPGA.

Co se týče ostatních prostředí, tak mají většinou drsnou konkurenci v podobě prostředích odvýrobců FPGA a jejich vývoj je výrazně omezen NDA informacemi (buď, že je dostanou a pak nemůžou dát databázi open, nebo je nemají

(nebo by to byl hooodně drahej koníček), navíc bys musel vyvíjet opravdu náročnou aplikaci, abys pak využil aspoň nějakou významnou část toho FPGA.

Co se týče ostatních prostředí, tak mají většinou drsnou konkurenci v podobě prostředích odvýrobců FPGA a jejich vývoj je výrazně omezen NDA informacemi (buď, že je dostanou a pak nemůžou dát databázi open, nebo je nemají  ). Ale četl jsem různé vědecké články, kde se psalo o jiných P&R než od výrobce. Poslední fáze a to překlad P&R databáze do bitstreamu má minimální až nulovou šanci na existenci, protože to je to čím může výrobce ovládat trh (a velmi znepříjemnit číňaňům reverzní inženýrství

). Ale četl jsem různé vědecké články, kde se psalo o jiných P&R než od výrobce. Poslední fáze a to překlad P&R databáze do bitstreamu má minimální až nulovou šanci na existenci, protože to je to čím může výrobce ovládat trh (a velmi znepříjemnit číňaňům reverzní inženýrství  ). Ale nějaké pokusy snad byly.

Klíčová slova: OpenPR, Debit, ReCoBus, JBits (+reference v článcích toto popisujících).

). Ale nějaké pokusy snad byly.

Klíčová slova: OpenPR, Debit, ReCoBus, JBits (+reference v článcích toto popisujících).

. Každopádně na pořádný GPU bys stejně potřeboval PCI připojení (dneska už asi PCIe) a to tuším třeba ani ty nejnižší Xilinx obvody řady 7 nemaj.

Jinak o grafiku se už někdo snažil, ale v té době to imho ještě neuzrálo. Dneska by už snad ty FPGA měly být dostatečně levný.

. Každopádně na pořádný GPU bys stejně potřeboval PCI připojení (dneska už asi PCIe) a to tuším třeba ani ty nejnižší Xilinx obvody řady 7 nemaj.

Jinak o grafiku se už někdo snažil, ale v té době to imho ještě neuzrálo. Dneska by už snad ty FPGA měly být dostatečně levný.

A co třeba 200000 LUT? WebPack podporuje třeba XC7K160T se 162240 LUT a 202800 FF nebo XC7A200T s 215360 LUT a 269200 FF. Nestačí? Stejně už to jsou obvody s kusovou cenou někde kolem $300-$500, takže tam asi nebude problém zaplatit si roční licenci ISE/Vivado za $3000-$5000 podle edice.

Obvody, které WebPack podporuje jsou uvedeny zde.

$5000 ročně za licenci je poměrně přijatelná cena. Roční mzdové náklady na jednoho zaměstnance s dvojnásobkem průměrné mzdy v ČR jsou přibližně 800 000 Kč. My třeba kromě jiného používáme vývojové prostředí Xilinx, Altera, k tomu ModelSim a Altium Designer, to je dohromady asi tak 400 000 Kč ročně za licence. Pořád je to jenom polovina mzdových nákladů na jednoho junior vývojáře.

$5000 ročně za licenci je poměrně přijatelná cena.Zalezi jak pro koho...

Roční mzdové náklady na jednoho zaměstnance s dvojnásobkem průměrné mzdy v ČR jsou přibližně 800 000 Kč. My třeba kromě jiného používáme vývojové prostředí Xilinx, Altera, k tomu ModelSim a Altium Designer, to je dohromady asi tak 400 000 Kč ročně za licence. Pořád je to jenom polovina mzdových nákladů na jednoho junior vývojáře.To chapu ze zamestnanec vyjde na milion rocne. Ale jak rikam, je rozdil jestli to pouziva ve firme, kde si na sebe videla, nebo doma pro zabavu, kde neceka zisk. V druhym pripade je $500 akceptovatelna cena, $5000 ne. Aspon teda pro me...

).

).

Nechci rozpoutávat žádnou šílenou nikam nevedoucí diskusi, protože to nemám rád a mám na práci důležitější věci, ale tohle mi nedá. Mám open-source rád, používám open-source nástroje všude, kde to má význam, ale tady to opravdu nechápu.

U vývojových nástrojů potřebuji v první řadě podporu a to dokonce dvojí. Jednak potřebuji zákaznickou podporu od dodavatele, za kterou bych platil obdobné částky jako za komerční licence teď, takže finanční úspora by byla nulová. Dále potřebuji slušnou podporu všech vlastností hardware. To není možné zajistit, pokud by GNU nástroje vyvíjel někdo jiný než výrobce společně s vývojem hardware. Již při návrhu křemíku FPGA se myslí na použitelnost a implementovatelnost ve vývojových nástrojích. Tak jako tak, zveřejněním zdrojových kódů implementačních nástrojů nebo detailních specifikací nutných pro vývoj takových nástrojů vyhodím milióny člověkohodin práce z okna. Prostě je daruji konkurenci. Tady se nejedná o softwarové patenty jak má vypadat nějaký debilní dialog nebo jak mohou být zakulacené rohy nesmyslného zařízení. Tady se jedná o miliardy investované do skutečného výzkumu a vývoje včetně základního.

Na druhou stranu u front-endu nikdo nikomu ve vývoji nebrání. Proč tedy už neexistuje množství dokonalých open-source nástrojů? Vždyť veškeré potřebné specifikace jsou volně dostupné. Znám jediného člověka, který v tomhle směru skutečně něco dokázal a to je Jan Decaluwe se svým MyHDL. Podobné je to se simulátory. V podstatě jediný použitelný open-source HDL simulátor je Icarus Verilog, který ale nepodporuje SystemVerilog. VHDL simulátory FreeHDL a GHDL jsou prakticky nepoužitelné. A to nemluvím třeba o smíšené simulaci.

.

.

Jednak potřebuji zákaznickou podporu od dodavatele, za kterou bych platil obdobné částky jako za komerční licence teď, takže finanční úspora by byla nulová.No sice nevím jaké problémy potřebuješ vyřešit, ale co jsem se koukal na fórum Xilinxu tak tam byl kotel dotazů, který je způsoben blobovitostí a uzavřeností jejich vývojových toolů (u opensource by ty chyby hledaly tisíce očí).

Dále potřebuji slušnou podporu všech vlastností hardware.Jo to byly ty druhý dotazy na fóru, které se často zaobírali sillicon errata (což GPL nevyřeší). To všech vlastností ale není pravda, protože já bych třeba chtěl udělat place and router FPGA běžícího přímo na tom FPGA. Pochybuju ale o tom, že by jejich placená podpora byla schopna ořezat par a map tak, aby se to vůbec vešlo do RAM na vývojové desce

.

.

Tak jako tak, zveřejněním zdrojových kódů implementačních nástrojů nebo detailních specifikací nutných pro vývoj takových nástrojů vyhodím milióny člověkohodin práce z okna.No přesto to Xilinx umožňuje. Syntézu není problém implementovat plně opensource a Xilinx toolům cpát standardizované netlisty. Vlastní MAP a PAR jde udělat v zásadě taky. Problém je, že u PARu IMHO blokuje Xilinx svým skoromonopolním (duopol?) postavením konkurenci použitím malé uzavřené databáze, přičemž konkurentní prostředí může používat pouze obrovité texťáky v dialektu lispu

. Kdyby bylo třeba sto výrobců FPGA s velmi podobnými vlastnostmi, tak prostě člověk přejde jinam. Zde to ale nejde. Xilinx tedy IMHO brzdí základní výzkum ostatních tím, že jim znemožňuje/znepříjemňuje jejich výzkum uzavřeností dokumentace (ledaže by byl ochoten dát NDA vlastně všem zájemcům - všichni by věděli všechno, ale nesměli by se o tom spoli bavit?

. Kdyby bylo třeba sto výrobců FPGA s velmi podobnými vlastnostmi, tak prostě člověk přejde jinam. Zde to ale nejde. Xilinx tedy IMHO brzdí základní výzkum ostatních tím, že jim znemožňuje/znepříjemňuje jejich výzkum uzavřeností dokumentace (ledaže by byl ochoten dát NDA vlastně všem zájemcům - všichni by věděli všechno, ale nesměli by se o tom spoli bavit?  ).

Navíc bych řekl, že porovnání potenciálních člověkohodin ostatních výzkumníků (masa) vůči výzkumníkům (špičkovým) Xilinxu je ve finále ve prospěch té otevřenosti mase.

).

Navíc bych řekl, že porovnání potenciálních člověkohodin ostatních výzkumníků (masa) vůči výzkumníkům (špičkovým) Xilinxu je ve finále ve prospěch té otevřenosti mase.

Prostě je daruji konkurenci.V případě GPL tomu tak není, pokud by se bralo to "darovat", tak pokud provede konkurence úpravu a distribuuje, tak musí "darovat" zpět, jinak je žalovatelná. Osobně bych samozřejmě nechtěl něco jako masky křemíku (na co taky, RepRap to stejně ještě neumí stisknout

), ale úplně by mě stačil logický popis všech registrů a jakou mají funkci. Když si kupuju PIC, ATMEGu, tak taky budu čekat, že budu schopen napsat program (ve strojovém kódu třeba), co bliká ledkou na výstupu. Datasheet je dnes už samozřejmost a Microchip stále prosperuje (OT: dokonce jsem si přes kámoše koupil jedno z nejnadupanějších PIC v DIL pouzdře a ještě jsem ho nepoužil

), ale úplně by mě stačil logický popis všech registrů a jakou mají funkci. Když si kupuju PIC, ATMEGu, tak taky budu čekat, že budu schopen napsat program (ve strojovém kódu třeba), co bliká ledkou na výstupu. Datasheet je dnes už samozřejmost a Microchip stále prosperuje (OT: dokonce jsem si přes kámoše koupil jedno z nejnadupanějších PIC v DIL pouzdře a ještě jsem ho nepoužil  ). Zajímavý, že u FPGA to nefunguje (a je to prakticky taky programovatelný prvek).

Co se týče miliard investovaných do výzkumu ne-hardwarové části, tak se mě zdá, že výsledek neodpovídá ceně

). Zajímavý, že u FPGA to nefunguje (a je to prakticky taky programovatelný prvek).

Co se týče miliard investovaných do výzkumu ne-hardwarové části, tak se mě zdá, že výsledek neodpovídá ceně  (nepodporované jazyky, pomalá implementace, nemožnost sledovat proměnné v simulátoru!).

(nepodporované jazyky, pomalá implementace, nemožnost sledovat proměnné v simulátoru!).

Na druhou stranu u front-endu nikdo nikomu ve vývoji nebrání. Proč tedy už neexistuje množství dokonalých open-source nástrojů?Protože na jeho použití si potřebuje uživatel koupit full nebo použít osekanou verzi firemního backendu. [joke] No vlastně se ani nedivím, že se do toho nikomu nechce. VHDL a Verilog jsou šílené jazyky

. [/joke]

Jinak ten problém není ani tak o těch frond-endech, jako o bitgenu. Já klidně budu navrhovat hardware bit po bitu v Poznámkovém bloku (na GALu jsem to i dělal

. [/joke]

Jinak ten problém není ani tak o těch frond-endech, jako o bitgenu. Já klidně budu navrhovat hardware bit po bitu v Poznámkovém bloku (na GALu jsem to i dělal  ), jenom bych nejdřív musel vědět, kterej bit to je.

), jenom bych nejdřív musel vědět, kterej bit to je.