Singularity (YouTube) je nejnovější otevřený film od Blender Studia. Jedná se o jejich první 4K HDR film.

Vyšla hra Život Není Krásný: Poslední Exekuce (Steam, ProtonDB). Kreslená point & click adventura ze staré školy plná černého humoru a nekorektního násilí. Vžijte se do role zpustlého exekutora Vladimíra Brehowského a projděte s ním jeho poslední pracovní den. Hra volně navazuje na sérii Život Není Krásný.

Společnost Red Hat představila Fedora Hummingbird, tj. linuxovou distribuci s nativním kontejnerovým designem určenou pro vývojáře využívající AI agenty.

Hru The Legend of Zelda: Twilight Princess od společnosti Nintendo si lze nově díky projektu Dusklight (původně Dusk) a reverznímu inženýrství zahrát i na počítačích a mobilních zařízeních. Vyžadována je kopie původní hry (textury, modely, hudba, zvukové efekty, …). Ukázka na YouTube. Projekt byl zahájen v srpnu 2020.

Byla vydána nová major verze 29.0 programovacího jazyka Erlang (Wikipedie) a související platformy OTP (Open Telecom Platform, Wikipedie). Detailní přehled novinek na GitHubu.

Po zranitelnostech Copy Fail a Dirty Frag přichází zranitelnost Fragnesia. Další lokální eskalace práv na Linuxu. Zatím v upstreamu neopravena. Přiřazeno ji bylo CVE-2026-46300.

Sovereign Tech Agency (Wikipedie) prostřednictvím svého fondu Sovereign Tech Fund podpoří KDE částkou 1 285 200 eur.

Google na včerejší akci The Android Show | I/O Edition 2026 (YouTube) představil celou řadu novinek: Gemini Intelligence, notebooky Googlebook, novou generaci Android Auto, …

Evropská komise by do léta mohla předložit návrh normy omezující používání sociálních sítí dětmi v zájmu jejich bezpečí na internetu. Prohlásila to včera předsedkyně EK Ursula von der Leyenová, podle níž řada zemí Evropské unie volá po zavedení věkové hranice pro sociální sítě. EU částečně řeší bezpečnost dětí v digitálním prostředí v již platném nařízení o digitálních službách (DSA), podle německé političky to však není dostatečné a

… více »Multiplatformní open source aplikace scrcpy (Wikipedie) pro zrcadlení připojeného zařízení se systémem Android na desktopu a umožňující ovládání tohoto zařízení z desktopu, byla vydána v nové verzi 4.0.

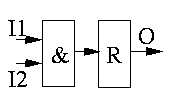

Všechny naše dosavadní obvody měly jeden společný rys. Neobsahovaly žádný paměťový prvek, takže hodnoty na výstupu byly závislé pouze na vstupních signálech. Takovéto obvody nazýváme kombinační. Skládají se pouze z logických členů (AND, OR, NOT, ...) a neobsahují zpětné vazby. Naproti tomu obvody, které obsahují paměťové prvky, se nazývají sekvenční. Jejich výstup není určen pouze vstupními signály, ale i vnitřním stavem obvodu (stavem jednotlivých paměťových prvků).

Jak jsme již naznačili minule (Jak se píše procesor - 3 (Procesy)),

jako paměťový prvek budeme využívat pouze registr (tzn. nebudeme tvořit

zpětné vazby v logice). Podívejme se, jak můžeme registr vytvořit pomocí

VHDL. Využijeme k tomu entitu example_2 podobnou entitě z

minulého dílu s tím rozdílem, že obsahuje navíc dva vstupní signály -

RESET a CLK.

ENTITY example_2 IS

PORT (

CLK, RESET: in std_logic;

I1, I2: in std_logic;

O: out std_logic

);

END example_2;

ARCHITECTURE arch_3 OF example_2 IS

BEGIN

p_1: process (RESET, CLK)

begin

if (RESET = '1') then -- asynchronni reset

O <= '0';

elsif (CLK'event and CLK = '1') then -- reakce na vz. hranu

O <= I1 and I2;

end if;

end process;

END arch_3;

Do procesu jsme vložili dvě sekce. Jednu reagující na reset a jednu na vzestupnou hranu hodin. VHDL zápis konkrétně znamená:

RESET '1', spusť první sekci

příkazů (to odpovídá činnosti asynchronního resetu v registru - nastavení

implicitních hodnot po startu systému).elsif) spusť druhou sekci příkazů, ale

pouze v případě, že došlo ke změně signálu CLK a tento signál

má hodnotu '1' (odpovídá náběžné hraně). Jinak řečeno, přiřaď

do výstupního signálu určenou logickou funkci, ale pouze v okamžiku

náběžné hrany hodin. Proto tento zápis vloží na konec cesty každého

výstupního signálu registr.Náš příklad bude tedy vypadat takto:

Podmíněný příkaz tvořící registr (if RESET... elsif

CLK...) je dobré brát pokud možno dogmaticky. Dnešní

programovatelné obvody důrazně dělí obvod na logiku a registry a každý

zásah do této části VHDL kódu může tuto strukturu narušit. Programovatelné

obvody také mají dedikované hodinové rozvody, proto, pokud si nejsme

jisti, je dobré používat v celém obvodu pouze jeden signál

CLK.

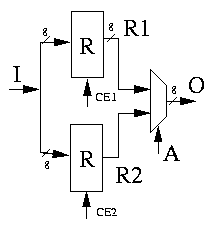

Nyní známe takřka všechno, co je třeba k napsání procesoru ve VHDL. Navrhněme proto další entitu - sadu registrů. Zvolme jednoduchou variantu sady čtyř osmibitových registrů, kde jedinou funkcí bude zápis do registrů a čtení z nich.

ENTITY register_set IS

PORT (

CLK, RESET: in std_logic;

I: in std_logic_vector(7 downto 0);

O: out std_logic_vector(7 downto 0);

ADDR: in std_logic_vector(1 downto 0);

WR: in std_logic

);

END register_set;

ARCHITECTURE behavioral OF register_set IS

signal R1, R2, R3, R4: std_logic_vector(7 downto 0);

BEGIN

p_1: process (RESET, CLK)

begin

if (RESET = '1') then -- asynchronni reset

R1 <= (others => '0');

R2 <= (others => '0');

R3 <= (others => '0');

R4 <= (others => '0');

elsif (CLK'event and CLK = '1') then -- reakce na vz. hranu

if WR = '1' then

if A = "00" then

R1 <= I;

elsif A = "01" then

R2 <= I;

elsif A = "10" then

R3 <= I;

else

R4 <= I;

end if;

end if;

end if;

end process;

O <= R1 when A = "00" else

R2 when A = "01" else

R3 when A = "10" else

R4;

END behavioral;

V entitě definujeme vstupní a výstupní signály. CLK a

RESET jsou důležité pro synchronizaci registrů.

I a O jsou vstupní a výstupní datové sběrnice,

A vybírá jeden ze čtyř registrů. Pomocí signálu

WR zapisujeme do jednotlivých registrů. Signál pro čtení

není třeba, na výstupní sběrnici je vždy hodnota aktivního registru.

V deklarační části architektury si definujeme čtyři pomocné osmibitové

signály, pomocí kterých vytvoříme vlastní registry. Hlavní část těla

architektury tvoří proces, který implikuje vytvoření registrů a realizuje

zápis. Kód nám říká, že v případě aktivního signálu WR má být

přiřazena hodnota sběrnice I do jednoho ze signálů

R1 - R4. Toto přiřazení se má provést pouze v

okamžiku náběžné hrany signálu CLK. Pro syntezátor to tedy

znamená vytvoření čtyř osmibitových registrů se vstupem I,

výstupem R1 - R4 a povolovacím signálem (chip

enable, CEx) tvořeným ze signálů WR a

A.

Výstup O je tvořen pomocí signálu WHEN. V

tomto případě to bude multiplexor, který vybírá výstup jednoho z registrů

v závislosti na adrese A.

Na obrázku je znázorněno zjednodušené schéma pro 2 registry:

Nástroje: Tisk bez diskuse

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()

začína to konečne vyzerať, že sa s tým dá niečo robiť... nenapíšete čitateľom nabudúce ukážkový 64bitový procesor? :)))

A teraz Vážne! Chcel som sa spýtať, či je existujú postupy na optimalizáciu hotových návrhov? Možno niekdo potrebuje usporiť a radšej by použil viacero lacnejších odvodov, ako pár drahšich.

.

V tomto serialu se pohybujeme v oblasti navrhu pro hradlova pole FPGA. To znamena, ze cely nas design nahrajeme obvykle do jednoho programovatelneho FPGA.

Jinak optimalizace provadi syntezator, ktery se snazi o co nejlepsi prevod naseho VHDL kodu do vnitrni struktury FPGA.

.

V tomto serialu se pohybujeme v oblasti navrhu pro hradlova pole FPGA. To znamena, ze cely nas design nahrajeme obvykle do jednoho programovatelneho FPGA.

Jinak optimalizace provadi syntezator, ktery se snazi o co nejlepsi prevod naseho VHDL kodu do vnitrni struktury FPGA.

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_arith.ALL;

ENTITY registers IS

GENERIC (

data_w : natural := 8;

addr_w : natural := 2;

num_regs : natural := 4

);

PORT (

res : IN std_logic;

clk : IN std_logic;

wr_en : IN std_logic;

addr : IN std_logic_vector(addr_w-1 DOWNTO 0);

data_in : IN std_logic_vector(data_w-1 DOWNTO 0);

data_out : OUT std_logic_vector(data_w-1 DOWNTO 0)

);

END registers;

ARCHITECTURE rtl OF registers IS

SUBTYPE reg_t IS std_logic_vector(data_w-1 DOWNTO 0);

TYPE reg_arr_t IS ARRAY (num_regs-1 DOWNTO 0) OF reg_t;

SIGNAL rg_ar_reg : reg_arr_t;

SIGNAL rg_ar_cmb : reg_arr_t;

SIGNAL rg_wr_cmb : std_logic_vector(num_regs-1 DOWNTO 0);

SIGNAL rg_sel_cmb : std_logic_vector(num_regs-1 DOWNTO 0);

BEGIN

gen_reg_array:

FOR i IN 0 TO num_regs-1 GENERATE

----

-- Registers Array

----

rg_ar_reg_proc:

PROCESS (res, clk)

BEGIN

IF (res = '1') THEN

rg_ar_reg(i) <= (OTHERS => '0');

ELSIF (clk'EVENT AND clk ='1') THEN

rg_ar_reg(i) <= rg_ar_cmb(i);

END IF;

END PROCESS rg_ar_reg_proc;

----

-- Register selection

----

sel_reg_cmb_proc:

PROCESS (addr, wr_en)

VARIABLE sel_v : std_logic_vector(num_regs-1 DOWNTO 0);

BEGIN

sel_v := (OTHERS => '0');

sel_v(conv_integer(unsigned(addr))) := '1';

rg_sel_cmb <= sel_v;

END PROCESS sel_reg_cmb_proc;

----

-- Registers array next

----

rg_ar_cmb_proc:

PROCESS (data_in, rg_ar_reg, rg_sel_cmb, wr_en)

BEGIN

IF (rg_wr_cmb(i)= '1' AND wr_en='1') THEN

rg_ar_cmb(i) <= data_in;

ELSE

rg_ar_cmb(i) <= rg_ar_reg(i);

END IF;

END PROCESS rg_ar_cmb_proc;

END GENERATE gen_reg_array;

----

-- Data output selection

----

data_sel_cmb_proc:

PROCESS (rg_ar_reg, addr)

VARIABLE addr_v : natural;

BEGIN

addr_v := conv_integer(unsigned(addr));

data_out <= rg_ar_reg(addr_v);

END PROCESS;

END rtl;

I tady je co vylepsovat. Napriklad registrovat vystup. Vasi poznamku o hokeji v casovani jsem nejak nepochopil. Co pipeline???

Jinak v tom Vasem kodu je chyba a nejde zkompilovat ("ADDR"!="A").

A tomu kody co je v clanku velmy dobre rozumim... Ale tomu kodu od profika uz nechapu. Aspom mam co studovat. Uvital bych vic takovych ukazek od profiku aby se clovek mel na cem ucit. Nejlepe aby kod byl komentovani...

A tomu kody co je v clanku velmy dobre rozumim... Ale tomu kodu od profika uz nechapu. Aspom mam co studovat. Uvital bych vic takovych ukazek od profiku aby se clovek mel na cem ucit. Nejlepe aby kod byl komentovani...