OCCT3D (Open CASCADE Technology) Open Source 8.0 bylo vydáno. OCCT3D (Wikipedie, GitHub) je objektově orientovaná knihovna pro 3D CAD, CAM nebo CAE. Používá se například v softwarech FreeCAD a KiCad.

Ve FreeBSD byla nalezena a již opravena 21letá zranitelnost CVE-2026-42511 v dhclient. Jedná se o vzdálené spuštění kódu (RCE). Útočník mající pod správou DHCP server může získat plnou kontrolu nad systémem FreeBSD pouze jeho připojením k místní síti.

Na čem aktuálně pracují vývojáři GNOME a KDE Plasma? Pravidelný přehled novinek v Týden v GNOME a Týden v KDE Plasma.

UBports, nadace a komunita kolem Ubuntu pro telefony a tablety Ubuntu Touch, vydala Ubuntu Touch 24.04-1.3. Současně oznámila, že nadcházející větší vydání 24.04-2.0 bude mít modernější webový prohlížeč.

Ploopy po DIY trackballech či sluchátkách představuje nový externí DIY trackpoint se čtyřmi tlačítky Bean. Obsahuje snímač Texas Instruments TMAG5273, spínače Omron D2LS-21 a řadič RP2040, používá firmware QMK. Schémata jsou na GitHubu; sadu lze předobjednat za 69 kanadských dolarů (bez dopravy a DPH).

Mozilla před dvěma týdny na svém blogu oznámila, že díky Claude Mythos Preview bylo ve Firefoxu nalezeno a opraveno 271 bezpečnostních chyb. Včera vyšel na Mozilla Hacks článek s podrobnějšími informacemi. Z 271 bezpečnostních chyb mělo 180 chyb vysokou závažnost, 80 chyb střední závažnost a 11 chyb nízkou závažnost. Celkově bylo v dubnu ve Firefoxu opraveno 423 bezpečnostních chyb. Čísla CVE nemusí být přiřazována jednotlivým chybám. CVE-2026-6784 například představuje 154 bezpečnostních chyb.

Před týdnem zranitelnost Copy Fail. Dnes zranitelnost Dirty Frag. Běžný uživatel může na Linuxu získat práva roota (lokální eskalaci práv). Na většině linuxových distribucí vydaných od roku 2017. Aktuálně bez oficiální záplaty a CVE čísla [oss-security mailing list].

Ačkoli je papež Lev XIV. hlavou katolické církve a stojí v čele více než miliardy věřících po celém světě, také on někdy řeší všední potíže. A kdo v životě neměl problémy se zákaznickou linkou? Krátce poté, co nastoupil do úřadu, musel papež se svou bankou řešit změnu údajů. Operátorka ale nechtěla uvěřit, s kým mluví, a Svatému otci zavěsila.

Incus, komunitní fork nástroje pro správu kontejnerů LXD, byl vydán ve verzi 7.0 LTS (YouTube). Stejně tak související LXC a LXCFS.

Google Chrome 148 byl prohlášen za stabilní. Nejnovější stabilní verze 148.0.7778.96 přináší řadu novinek z hlediska uživatelů i vývojářů. Vypíchnout lze Prompt API (demo) pro přímý přístup k AI v zařízení. Podrobný přehled v poznámkách k vydání. Opraveno bylo 127 bezpečnostních chyb. Vylepšeny byly také nástroje pro vývojáře.

Prozatím lze všechny příkazy, které jsme si ukazovali, zařadit mezi tzv. souběžné příkazy - všechny se provádí najednou bez ohledu na pořadí. V obvodové realizaci to ukazuje na paralelní obvody. Pomocí procesu můžeme použít příkazy sekvenční, kde naopak pořadí příkazů hraje důležitou roli. Proces sám o sobě je jeden souběžný příkaz.

Sekvenční zpracování příkazů v procesu se řídí následujícími pravidly:

Proces můžeme také chápat jako myšlenkovou přípravu na vytvoření

signálů. Nejlepší bude ukázat si činnost procesu na příkladu.

Předpokládejme dvě různé architektury k entitě example_1

(deklaraci entity neuvádím), která má pouze jeden výstupní signál

O:

ARCHITECTURE arch_1 OF example_1 IS BEGIN O <= '1'; O <= '0'; END arch_1;

ARCHITECTURE arch_2 OF example_1 IS

BEGIN

p_1: process

begin

O <= '1';

O <= '0';

end process;

END arch_2;

V prvním případě se snažíme do výstupního signálu O

napojit současně dvě hodnoty - log. '1' a log. '0'. To by mohlo mít v

reálném obvodu katastrofální následky. Pokud například uvažujeme logiku,

kde log. '1' znamená připojení na +5V a log. '0' připojení na zem,

zapisujeme tímto kódem zkrat. Ve druhém případě se ale příkazy

zpracovávají sekvenčně. Druhý přiřazovací příkaz "přebije" první a na

výstupu O bude '0';

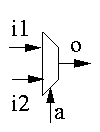

V procesu není možné použít souběžný příkaz when, místo

něj můžeme aplikovat sekvenční příkaz if. Uvažujme příklad

z minulého

dílu, kde jsme vytvořili multiplexor pomocí příkazu

O <= I1 when A = '0' else I2

V procesu by vypadal zápis tohoto multiplexoru následovně:

p_1: process (I1, I2, A)

begin

if A = '0' then

O <= I1;

else

O <= I2;

end if;

end process;

Zaměřme se nyní více na syntaxi procesu. Před klíčovým slovem

process je návěští, v našem případě p_1. To je

důležité pro případnou identifikaci procesu v průběhu simulace nebo

syntézy. Za klíčovým slovem process je tzv. sensitivity

list. V něm říkáme simulátoru, kdy má proces spustit a obnovit hodnoty

výstupních signálů. Tento výpočet provede simulátor právě při změně

libovolného signálu obsaženého v sensitivity listu. V praxi to znamená, že

do sensitivity listu je třeba zapsat všechny signály, které do procesu

vstupují. V našem případě jsou to signály I1, I2

a A.

Vezměme nyní následující proces:

p_1: process (I1, I2, A)

begin

O <= I2;

if A = '0' then

O <= I1;

end if;

end process;

Tento zápis je zcela identický s předchozím procesem. Nejdříve do

výstupního signálu O přiřazujeme signál I2, ale

v případě, že je hodnota signálu A '0', dostane se ke slovu

přiřazovací příkaz O <= I1. Výsledek je tedy

opět stejný multiplexor.

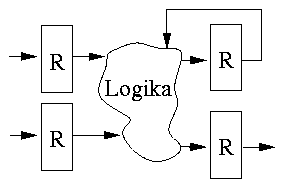

Nyní uděláme malou odbočku k tomu, jakým způsobem psát design. Budeme

hovořit o synchronním designu, tzn. v obvodu se vyskytuje jediný hodinový

signál clk. Dnešním standardem je jasně rozdělit design na

registry (paměťové prvky, realizovatelné např. klopným obvodem D) a

kombinační logiku (prvky AND, OR, NOT...) bez cyklů. Registry jsou všechny

taktovány na stejnou (např. náběžnou) hranu clk. V okamžiku

této náběžné hrany se přepíše signál ze vstupu registru na výstup.

Následuje cesta signálu přes kombinační logiku, než dorazí na vstup

dalšího registru. Jakmile všechny signály projdou přes logiku a ustálí se,

může přijít další náběžná hrana hodin a celý proces se opakuje.

Z toho vyplývá i maximální frekvence hodin. Jejich perioda musí být minimálně taková, aby se signál ustálil i na nejdelší cestě v celém obvodu. Pokud tedy taktujeme např. procesor na 1600 MHz, znamená to, že nejdelší cestou (mezi dvěma registry spojenými pouze logikou) v jeho designu projde signál za méně než 0,625 nanosekundy.

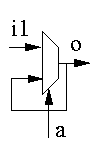

Podívejme se nyní na následující proces:

p_1: process (I1, I2, A)

begin

if A = '0' then

O <= I1;

end if;

end process;

Pokud má signál A hodnotu '0', bude na výstupu

I1. Co ale když bude A '1'? To potom znamená

zachovat na výstupu aktuální hodnotu. A zde se dostáváme k jádru problému.

K zachování hodnoty potřebujeme paměťový prvek. V tomto konkrétním případě

bude tvořen zpětnou vazbou, např. takto:

A právě tato zpětná vazba (latch) není přípustná. Proč je vlastně zpětná vazba v logice problém? Např. může zmást syntezátor při počítání délky cesty v obvodu. Obvod potom může fungovat, ale také nemusí (což většinou nastane v nejméně vhodnou dobu).

Jaký z toho plyne závěr? V příkazu if (pokud proces

netvoří registr, ukážeme si příště) je třeba vždy pokrýt všechny stavy

vstupních signálů pro výstupní signály. Jinými slovy, každý výstupní

signál musí mít jasně definovanou hodnotu pouze v závislosti na vstupních

signálech. Podobný problém může nastat i u souběžného signálu

when - tam je také vhodné vždy uvádět klauzuli

else.

Nástroje: Tisk bez diskuse

Tiskni

Sdílej:

![]()

![]()

![]()

![]()

![]()

![]()